# Fluxless bonding of silicon to alumina substrate using electroplated eutectic Au-Sn solder

# Fluxless Bonding of Silicon to Alumina Substrate Using Electroplated Eutectic Au-Sn Solder

Jong S. Kim, Won S. Choi\*, Dongwook Kim<sup>+</sup>, Andrei Shkel<sup>#</sup>, and Chin C. Lee

Electrical Engineering and Computer Science

Materials Science and Engineering

"Mechanical and Aerospace Engineering

University of California

Irvine, CA 92697-2660

cclee@uci.edu

\* Now with Samsung Electronics, Korea

\* Now with Intel Corporation, Folsom, CA

#### **Abstract**

Large 6mm x 9mm silicon dice have been successfully bonded on alumina substrate with electroplated Au80Sn20 eutectic alloy. Eutectic AuSn is one of the best known hard solders having excellent fatigue-resistance and mechanical properties. A fluxless bonding process in 50militorrs of vacuum environment is presented. Vacuum environment is employed to prevent tin oxidation during the process. The oxygen content is expected to be reduced by a factor of 15,200, comparing to bonding in air. One of the challenges in silicon-to-alumina bonding is the large mismatch in thermal expansion between silicon of 2.7x10<sup>-6</sup>ppm/°C and alumina of 7x10<sup>-6</sup>ppm/°C. Electroplating method is used to build multi-layer solder. It is an economical alternative to vacuum deposition method and can produce thick solders. Joints fabricated are examined using Scanning Electron Microscope (SEM), and Energy Dispersive X-ray Spectroscopy (EDX). It is found that proper bonding condition is needed to turn the stacked layers into a uniform AuSn eutectic alloy. Nearly void-free joints are achieved and confirmed by a Scanning Acoustic Microscope (SAM). To evaluate the reliability of the solder joint and the bonded structure, samples will go through thermal cycling test to determine failure modes. Microstructural changes of the solder joints during thermal cycling test will also be investigated.

### 1. Introduction

Many semiconductor device chips are bonded to ceramic (alumina) substrates using solders. Popular solders in the industry are soft solders such as eutectic SnPb, SnAg and SnCu. These solders have relatively low melting temperature and high thermal conductivity. However, they are not mechanically strong and are likely to incur thermal fatigue and creep [1]. The eutectic Au80Sn20 alloy, which is a hard solder, has been widely used in photonic packaging due to its high mechanical strength and free of thermal fatigue and free of creep [2-4]. One difficulty in using eutectic AuSn solder is that the parts to be bonded must have relatively close thermal expansion coefficient because its range of plastic strain is very small. Thus, it has always been a challenge to bond large silicon chips to alumina substrates because of thermal expansion mismatch, 2.7x10 <sup>6</sup>ppm/°C for silicon versus 7x10<sup>-6</sup>ppm/°C for alumina. We had previously demonstrated this possibility using AuSn preform without using any flux [2].

In this work, we look into electroplating processes to fabricate the solder structure directly on the alumina substrates. The solder structure is designed so that the bonding process can be performed without the use of any flux. Fluxless feature is critically important in achieving void-free joints in bonding

large chips because flux and residues can be easily trapped in the joint, causing voids. Fluxless technique has become more important because there are more devices such as MEMS and photonic that cannot accept flux. In some applications, flux residues could cause reliability problem, if not completely removed [5].

Au-Sn alloys can be produced in several ways such as the use of solder preforms, vacuum deposition technique. and electroplating method. Solder preforms, popular for some applications, have difficulty in alignment and get oxidized easily before and during bonding [6]. Thermal (or electron-beam) evaporation in high vacuum can deposit metal thin films that are very clean and uniform with excellent thickness control. Thermal evaporation in vacuum also makes it possible to inhibit tin oxidation during the deposition process, and thus allow the tin layer to be capped with an oxygen barrier layer such as gold in the same vacuum cycle [7]. However, the deposition process and equipment maintenance are costly for making thick layers such as 10 µm and above. To find an economical alternative, we turn to the electroplating processes. An additional advantage of electroplating is its low process temperature (room temperature~60°C) that reduces unwanted diffusion and reaction between Au and Sn, which are more likely to occur in vacuum deposition process due to higher substrate temperature. The use of electroplating processes makes patterning of solder structure possible.

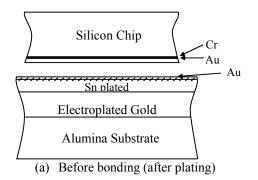

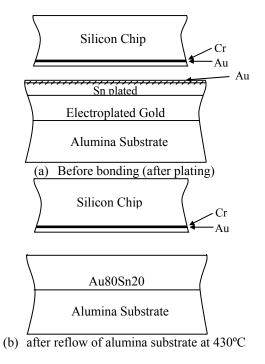

In the first step of our fluxless bonding processes, 11µm Au is electroplated over 10mm x 12mm alumina substrate, followed by 7.5µm Sn with 0.1µm Au capping layer for achieving eutectic composition. The thin Au capping layer, when electroplated, reacts with Sn to form AuSn<sub>4</sub> intermetallic compound immediately and works to prevent oxidation of inner Sn to achieve fluxless feature as proven in our previous research [8, 9]. The silicon chips, 6mm x 9mm in size, are coated with 0.03µm Cr and 0.1µm Au deposited in vacuum. Cr act as an adhesion layer and Au layer is to prevent Cr oxidation. Bonding is performed in a vacuum chamber that can be pumped to 50 militorrs. Three bonding conditions are used and compared. In the first method, fluxless bonding is conducted at 320°C. Secondly, bonding is performed at higher process temperature of about 430°C without reflow. Lastly, electroplated alumina substrate is loaded in a vacuum chamber and undergoes a reflow process at temperature above 430°C, followed by 320°C bonding process to silicon chips. Higher temperature is used for second and third method to ensure that the plated Au-Sn-Au structure turns into a mixture containing adequate

molten phase during the bonding. All processes are done without using any flux. i.e. flux-free.

In this paper, we report our success in fluxless bonding technique between silicon chip and alumina substrate using electroplated eutectic Au80Sn20 structures. The fluxless bonding process in vacuum environment and resulting joint are presented. SEM and SAM were used to evaluate the quality of the joint. To evaluate the reliability of the solder joint and the bonded structure, samples will go through thermal cycling test. Microstructural changes of the solder joints during thermal cycling test will be investigated and assessed.

We first present Gold-Tin binary system for better understanding. Experimental design and procedures are described. Experimental results are reported and discussed. A short summary with future plan is then given.

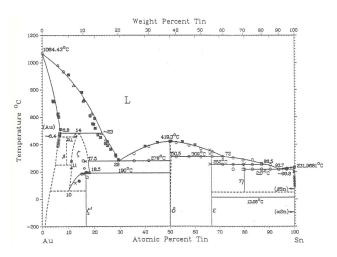

Figure 1 - Tin-Gold phase diagram [10]

### 2. Gold-Tin Binary System

The gold-tin phase diagram [10] as shown in Figure 1 depicts a complex combination of eutectic and peritectic systems. Gold-tin alloy system is so complicated with five intermediate phases appearing: ζ phase, Au<sub>5</sub>Sn, AuSn, AuSn<sub>2</sub>, and AuSn<sub>4</sub>. The ζ phase (hexagonal close-packed crystal structure) is homogeneous between 12 and 16 at. % Sn. The intermetallic compound AuSn (hexagonal NiAs structure) has a very narrow range of solubility. The homogeneity range of AuSn<sub>2</sub> (orthorhombic) and AuSn<sub>4</sub> (orthorhombic PtSn<sub>4</sub> structure) are also very narrow. First, the liquid phase is identified as L. Second, the L  $\leftarrow \rightarrow [\zeta + AuSn]$  eutectic occurs at 278°C with 29.5 at. % Sn. This is the most commonly used eutectic of 20 wt.% Sn and 80 wt.% Au. Third, the δ phase is determined as the AuSn intermetallic that has a melting point of 419.3°C. The homogeneity range extends from 50.0 to 50.5 at.% Sn. Fourth, the ε phase is identified at the AuSn<sub>2</sub> intermetallic compound. The temperature of the peritectic [L +  $\delta$ ]  $\leftarrow \rightarrow$  ε reaction is 309°C, giving the liquidus composition of about 72 at.% Sn. The homogeneity range of this phase is very narrow. Fifth, the η phase is found to be as the AuSn<sub>4</sub> compound. The temperature of the peritectic  $[L + \varepsilon] \leftarrow \eta$ reaction is 252°C, giving the liquidus composition of about 88.5 at.% Sn. The L  $\leftarrow \rightarrow$  [ $\eta + \beta Sn$ ] eutectic reaction occurs at 93.7 at.% Sn at 217°C, called as second eutectic reaction. Lastly, the

allotropic temperature between two terminal solid solutions of  $(\beta\text{-Sn})$  and  $(\alpha\text{-Sn})$  is 13.05°C. The  $(\beta\text{-Sn})$  solid solution has a solubility up to 0.2 at. % Au in  $\beta$ -Sn. The  $(\alpha$ -Sn) solid solution has a very limited solid solubility, that is, less than 0.006 at. % Au in  $\alpha$ -Sn.

### 3. Experimental Procedure

To perform fluxless bonding, thin Cr layer of 0.03 µm and Au layer of 0.1 µm are deposited on a Si wafer in a high vacuum e-beam evaporator (3×10<sup>-6</sup> torr). Cr acts as an adhesion layer and the Au layer is to prevent Cr oxidation. The wafer with Cr/Au layers is diced into 6 mm x 9 mm pieces using Tempress dicing saw. Alumina substrate with Ti/W/Au metallization is first electroplated with 11µm of Au. The Au plating bath is neutral non-cyanide plating solution at pH 7 based on sulfite complex with mild agitation. The current density and process temperature were 4.6mA/cm<sup>2</sup> and 60°C, respectively. It is then followed by 7.5µm of Sn plating in a stannous tin based bath at 21.5mA/cm<sup>2</sup>. Very thin Au capping layer (0.1µm) is plated over alumina/Au/Sn substrate mainly to prevent the oxidation of the Sn. To prevent Sn oxidation prior to gold capping layer plating, the sample is rinsed in acid solution right after Sn plating. The alumina substrate is diced into 10mm x 12mm. The Si chip and alumina substrate are held together with a static pressure of 50 psi (0.35 Mpa) using a graphite fixture to ensure intimate contact. The assembly is then loaded into a vacuum chamber built in house and pumped down to 50 militorr vacuum environments. The furnace is turned on and the temperature of the fixture is monitored with a thermocouple. Three bonding conditions are employed. First, the vacuum chamber is heated to optimum temperature for bonding, 320°C using a temperature controller. The assembly was then allowed to cool naturally to room temperature in vacuum ambient. Secondly, bonding is conducted at higher process temperature of 430°C in the same vacuum ambient. Bonding time is much longer than that of the first condition. In third the alumina substrate (alumina/Au/Sn/Au) undergoes a reflow process at 430°C, followed by fluxless bonding at 320°C. To evaluate the quality of the joints, SAM was used to identify voids in the solder joints. SEM and EDX were employed to characterize the composition microstructures of solder joints. Re-melting temperatures of several samples are to be measured by debonding test.

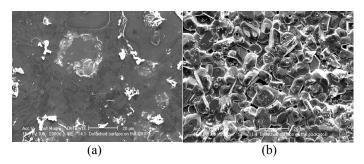

# 4. Experimental Results and Discussions A. 320°C bonding process – bonding failure

Si chip and alumina substrate were detached after bonding process at 320°C. Figure 2 displays secondary electron images on the detached surface of si side and alumina side, respectively. On Si side, mainly Si with little amount of Cr is detected by EDX analysis, while certain type of AuSn intermetallic compounds were detected on alumina side. This reveals that broken interface is between Si/Cr and AuSn intermetallic compound. Process temperature of 320°C seems not high enough to liquefy the whole solder joint, but only partly dissolves the joint. Three

stacked electroplating layers of Au/Sn/Au need to react each other during the bonding process to reach a uniform composition of Au80Sn20, but some portion of the joints still remains as a solid material, and cannot be attached to silicon chip leading to a bonding failure. To reach a uniform composition of eutectic Au80Sn20, Sn has to pass through some intermediate phases such as AuSn<sub>4</sub>, AuSn<sub>2</sub>, and AuSn while Sn is diffusing into Au layer. AuSn<sub>2</sub> and AuSn<sub>4</sub> are expected to melt below 320°C, but AuSn does not melt at our process temperature. The melting temperature of AuSn intermetallic compound (δ phase) is 419°C, and it is obvious that 320°C process temperature is too low, providing the existence of AuSn intermetallic compound. Thus, higher process temperature is desired to ensure that the plated Au-Sn-Au structure turns into a mixture containing adequate molten phase during the bonding.

Figure 2 - Top view of the detached sample after 320°C bonding process (a) Si side (b) alumina side

## B. 430°C bonding process

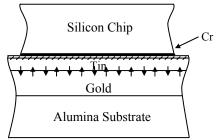

Based upon the results that we got from 320°C bonding process, we move to much higher process temperature of 430°C. Above 419°C, all major three AuSn intermetallic compounds are to be dissolved; AuSn (419°C), AuSn<sub>2</sub> (309°) and AuSn<sub>4</sub> (252°C). High enough temperature and long enough reflow time enable the joint to become a very uniform composition of Au80Sn20. As shown in Figure 3(b), as the temperature reaches 232°C of Sn melting temperature, Sn starts to melt to react with Au layer below and generate several kinds of AuSn intermetallic compounds. As the temperature further increases to peak temperature of 430°C, all the possible compound layers are dissolved to react with Si chip to form a strong joint. After cooling down to room temperature, the joint eventually becomes very strong as displayed in Figure 3 (c).

(b) from melting temperature of Sn to peak temperature

Figure 3 - Principle of the fluxless bonding at 430°C

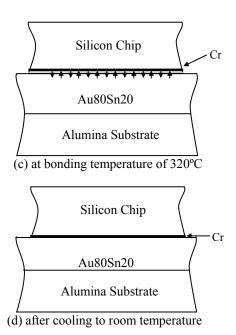

# C. 320°C bonding after reflow process at 430°C

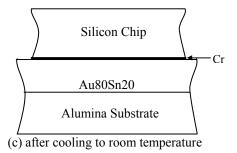

We propose another way to bond silicon chip to alumina substrate. The sample undergoes a reflow process at 430°C, followed by bonding at 320°C. Electroplated alumina substrate is reflowed inside a vacuum chamber at 430°C to turn the stacking layer structure of Au/Sn/Au into uniformly distributed eutectic AuSn alloy as shown in Figure 4 (b). This substrate and si chip are held together for fluxless bonding conducted at 320°C, about 40°C higher than eutectic AuSn melting temperature. Final joint is displayed in Figure 4(d).

Figure 4 - Principle of the fluxless bonding at 320°C after reflow process at 430°C

# D. Joint analysis by SEM and SAM

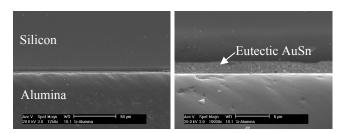

Figure 5 shows secondary electron image of the joint with lower magnification (a) and higher magnification (b). Nearly perfect joint without any big void is shown. Solder layer thickness is down to about 3µm due to applied high pressure during the bonding process. EDX data shows that final joint composition is very close to eutectic Au80Sn20.

Figure 5. SEM image of the joint at (a) low magnification (x1,250) and (b) high magnification (10,000x)

The Transmission SAM analysis was performed on samples of eutectic AuSn joint to evaluate the quality of the joint. The SAM operates at an acoustic frequency between 100~150 MHz. This is very useful for non-destructive testing of integrated circuit and optically opaque samples. The microscope has the ability to image internal features of a sample showing the presence of manufacturing and processing defects (voids). Voids are seen as high contrast images because of the mismatch in acoustic impedance between the solder material and the void. The acoustic image in Figure 6 shows that good quality joint with some small voids. We expect to produce nearly void-free joints with further effort to refine our processes. The solder joint is quite strong. We tried to break the joint with a hand tool but the silicon chip always broke first.

Figure 6 - SAM image of the eutectic AuSn joint

### 5. Summary

In summary, we have successfully developed fluxless bonding process between silicon chip and alumina substrate. Electroplating processes were employed to manufacture eutectic AuSn structures for achieving fluxless joints of high quality. Electroplated Au/Sn/Au layers on alumina substrate becomes a uniform eutectic AuSn composition either by high temperature bonding process or by reflow process before bonding. Electroplating method in fabricating thick solder layers is proven to be cost effective than the thermal evaporation technique in high vacuum. Another advantage of electroplating lies on the fact that very thicker films can be deposited. Proper choice of bonding layer and bonding condition can overcome the large mismatch in thermal expansion coefficient between silicon and alumina. This method and the use of electroplated eutectic AuSn offer the packaging industry a good economical alternative to other lead-free soft solders. This new fluxless process using electroplated eutectic AuSn structures could play an important role in various applications such as photonic devices, MEMS devices, sensor devices, and biomedical devices, where the use of fluxes is not allowed.

### References

- 1. D. R. Frear, S. N. Burchett, H. S. Morgan, and J. H. Lau, editors, The mechanics of solder alloy interconnects, Van Nostrand Reinhold, 1994.

- Goran Matijasevic, Chen Y. Wang, and Chin C. Lee, "Void Free Bonding of Large Silicon Dice Using Gold-Tin Alloys," *IEEE Trans. Components, Hybrids, and Manufacturing Tech.*, 13, pp. 1128-1134, 1990.

- 3. H. Mavoori, A. G. Ramirez, and S. Jin, "Lead-Free Universal Solders for Optical and Electronic Devices," *J. Electronic Materials*, 31, pp. 1160, 2002.

- Robert S. Forman, and Gerard Minogue, "The Basics of Wafer-Level AuSn Soldering," *Chip Scale Review*, 8, pp. 55-59, 2004.

- 5. F. Zhang, M. Li, W. T. Chen, and K. S. Chian, "An investigation into the effects of Flux Residues on Properties of Underfill Materials for Flip Chip Packages," *IEEE Trans. Components and Packaging Tech.*, pp. 233-238, 2002.

- 6. W. Sun, D. G. Ivey, "Development of electroplating solution for codeposition Au-Sn alloys", *Materials Science and Engineering B*, 65, pp. 111-122, 1999.

- 7. Chin C. Lee, Chen Y. Wang and Goran Matijasevic, "A New Bonding Technology Using Gold and Tin Multilayer Composite Structures," *IEEE Trans. Components, Hybrids, and Manufacturing Tech*, 14, pp. 407-412, June 1991.

- Dongwook Kim, Jongsung Kim, Gow L. Wang, and Chin C. Lee, "Nucleation and growth of intermetallics and gold clusters on thick thin layers in electroplating process," Materials Science and Engineering A, 393, pp. 315-319, 2005

- 9. Jongsung Kim, Dongwook Kim, and Chin C. Lee, "Fluxless flip-chip solder joint fabrication using electroplated Sn-rich Sn-Au structures," *IEEE Advanced Packaging*, in press, 2005.

- 10. H. Okamoto and T. B. Massalski, Phase Diagram of Binary Gold Alloys, Mtelas Park, OH: ASM International, 1987, pp. 2778-289.